Quartus II 是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,Quartus II内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II 是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,Quartus II内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

| 相关软件 | 版本说明 | 下载地址 |

|---|---|---|

| UEStudio | 中文版 | 查看 |

| AAuto Quicker | 官方版 | 查看 |

| Anaconda | 官方版 | 查看 |

| Atom | 中文版 | 查看 |

Quartus II可以在Windows、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

Maxplus II 作为Altera的上一代PLD设计软件,由于其出色的易用性而得到了广泛的应用。目前Altera已经停止了对Maxplus II 的更新支持,Quartus II 与之相比不仅仅是支持器件类型的丰富和图形界面的改变。Altera在Quartus II 中包含了许多诸如SignalTap II、Chip Editor和RTL Viewer的设计辅助工具,集成了SOPC和HardCopy设计流程,并且继承了Maxplus II 友好的图形界面及简便的使用方法。

Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

对于FPGA、CPLD以及结构化ASIC设计,quartus ii 11.0是性能和效能首屈一指的设计软件。软件支持Altera名为Qsys的系统级集成工具新产品,实现了对Stratix® V FPGA系列的扩展支持,并且采用增强后的调试方案加快了电路板开发。

Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:

1、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

2、芯片(电路)平面布局连线编辑;

3、LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

4、功能强大的逻辑综合工具;

5、完备的电路功能仿真与时序逻辑仿真工具;定时/时序分析与关键路径延时分析;可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

6、支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

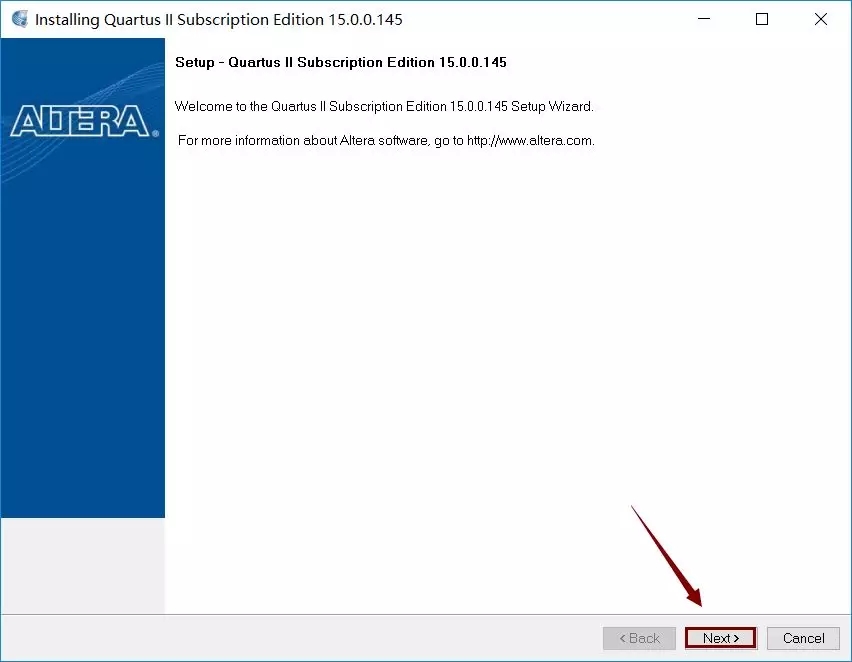

在本网站下载Quartus II软件安装包,进入软件安装界面,点击“Next”。

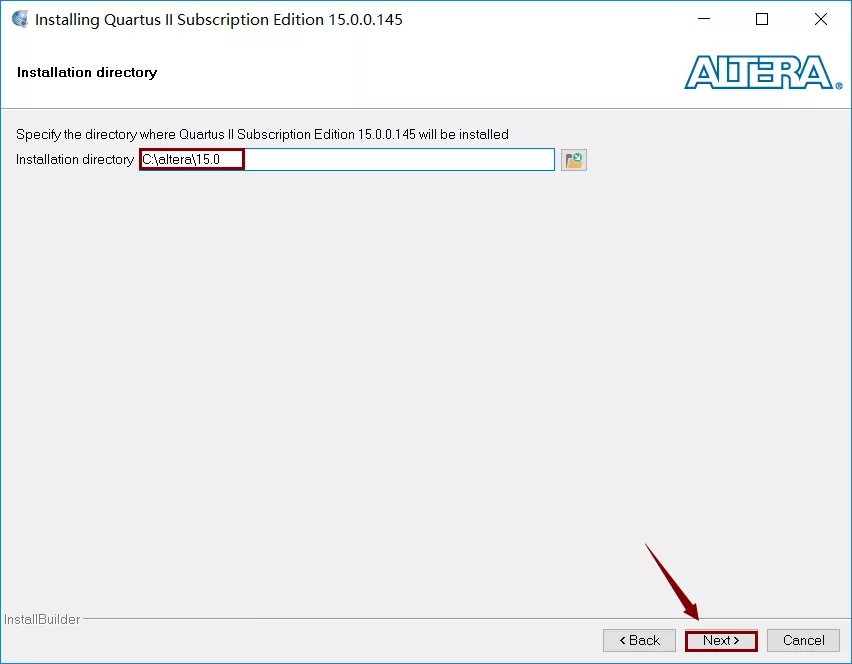

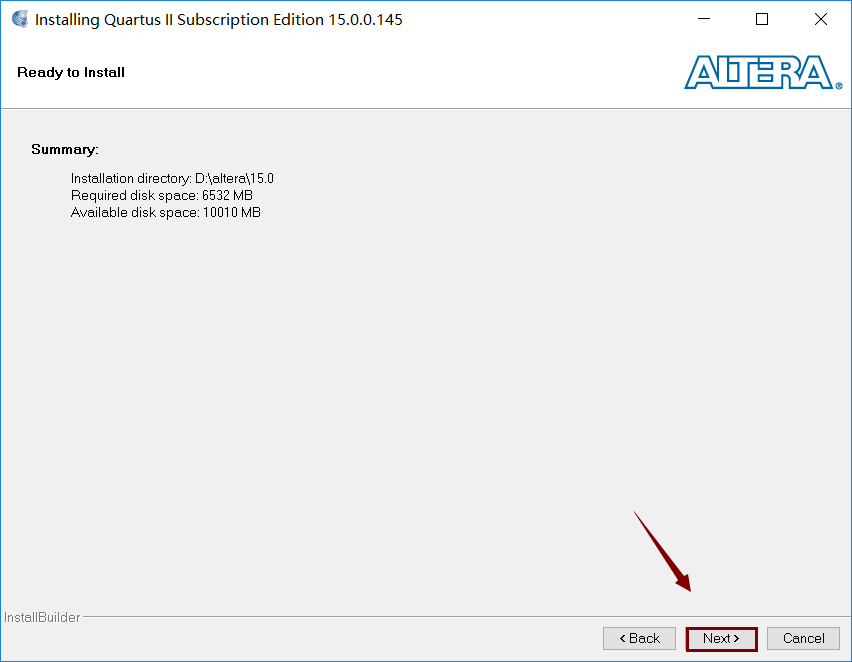

选择你要安装的路径,但请注意不要选择带有中文路径安装

点击“Next”开始安装。

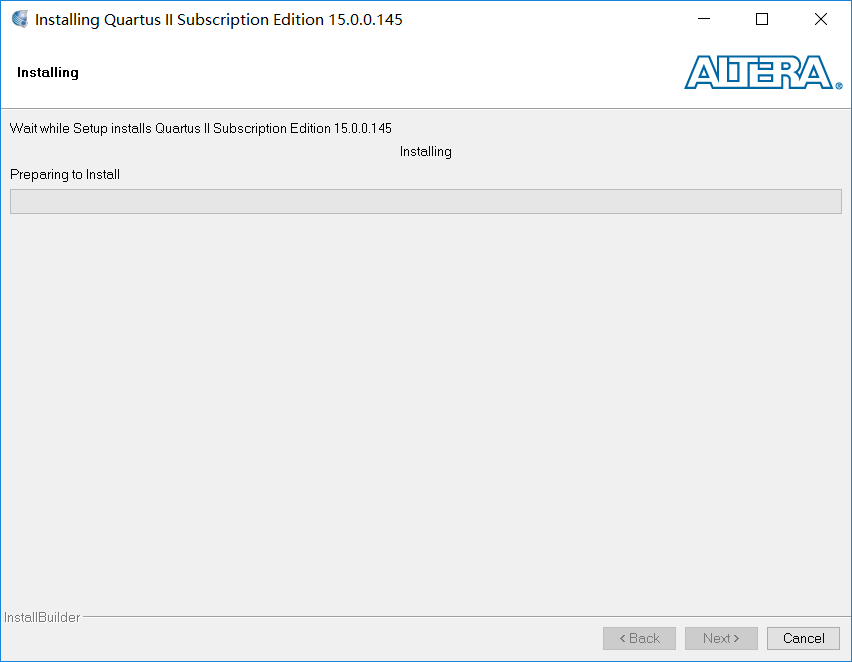

软件正在安装中,请等待

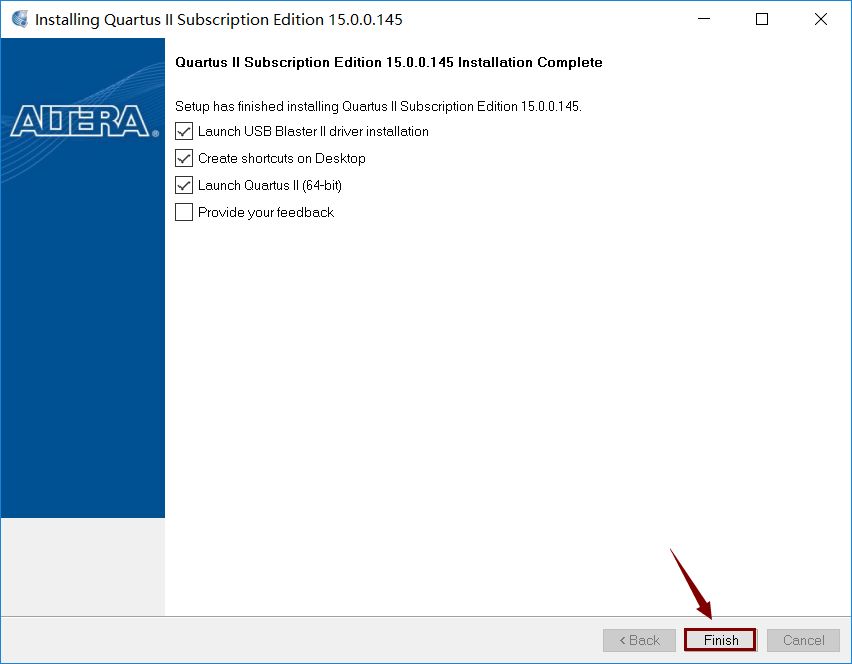

软件安装步骤,点击“Finish”。

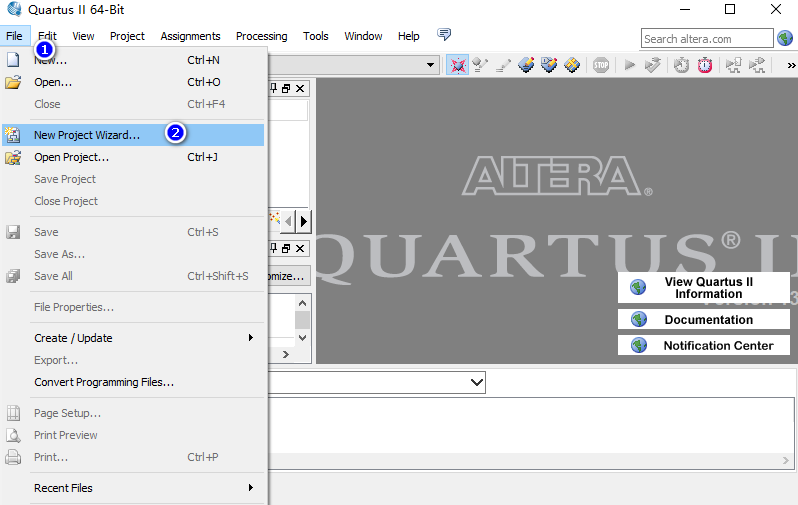

打开软件,点击“File——New Project Wizard...”新建一个项目

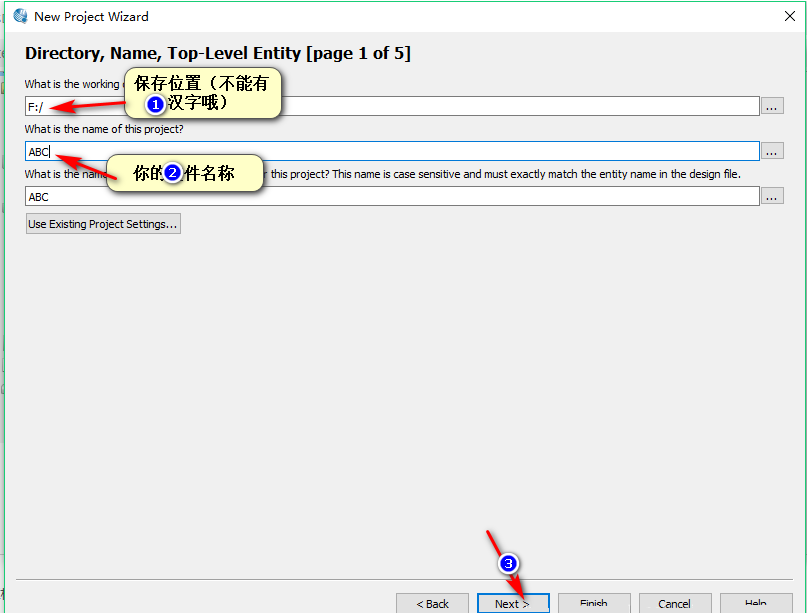

这里会弹出来一个框,然后点击“next”得到下面这个图

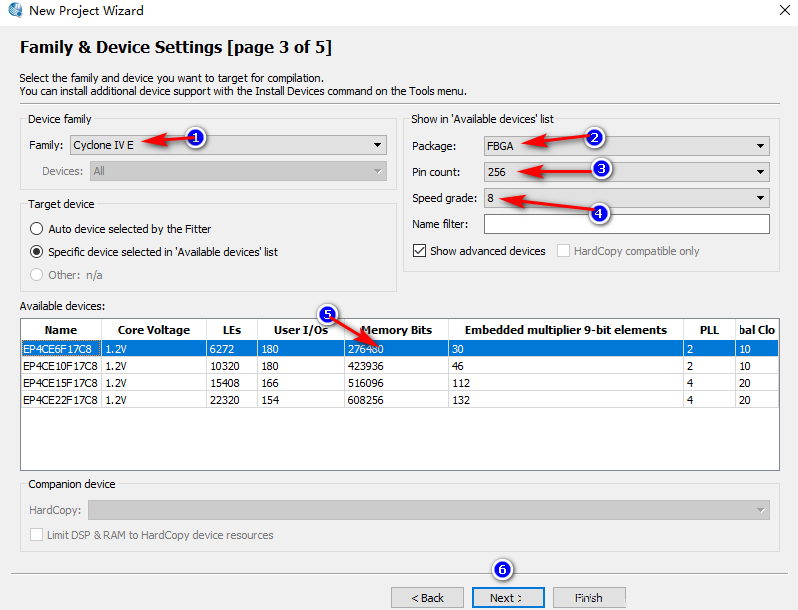

这里根据图示选择后点击“next”,都需要点一下哦

全部设置完成后点击“finsh”

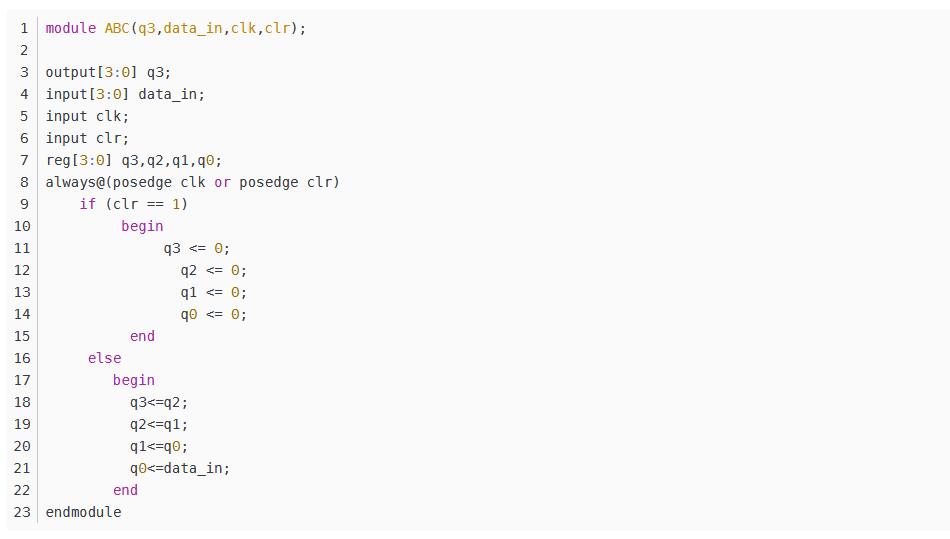

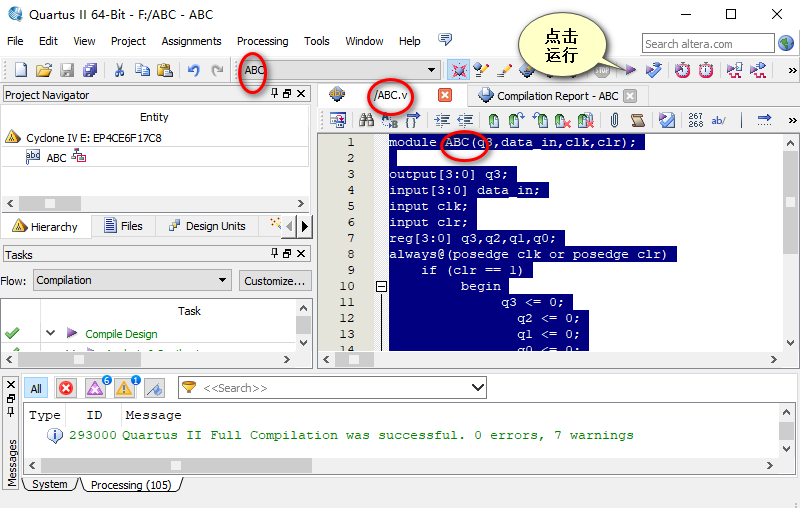

把你的代码写入新建的文件当中,如上是我的代码,注意代码的名称要和你的文件名称一样,否则会有错误

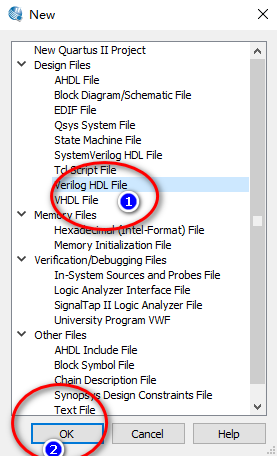

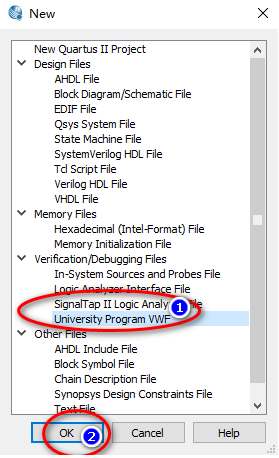

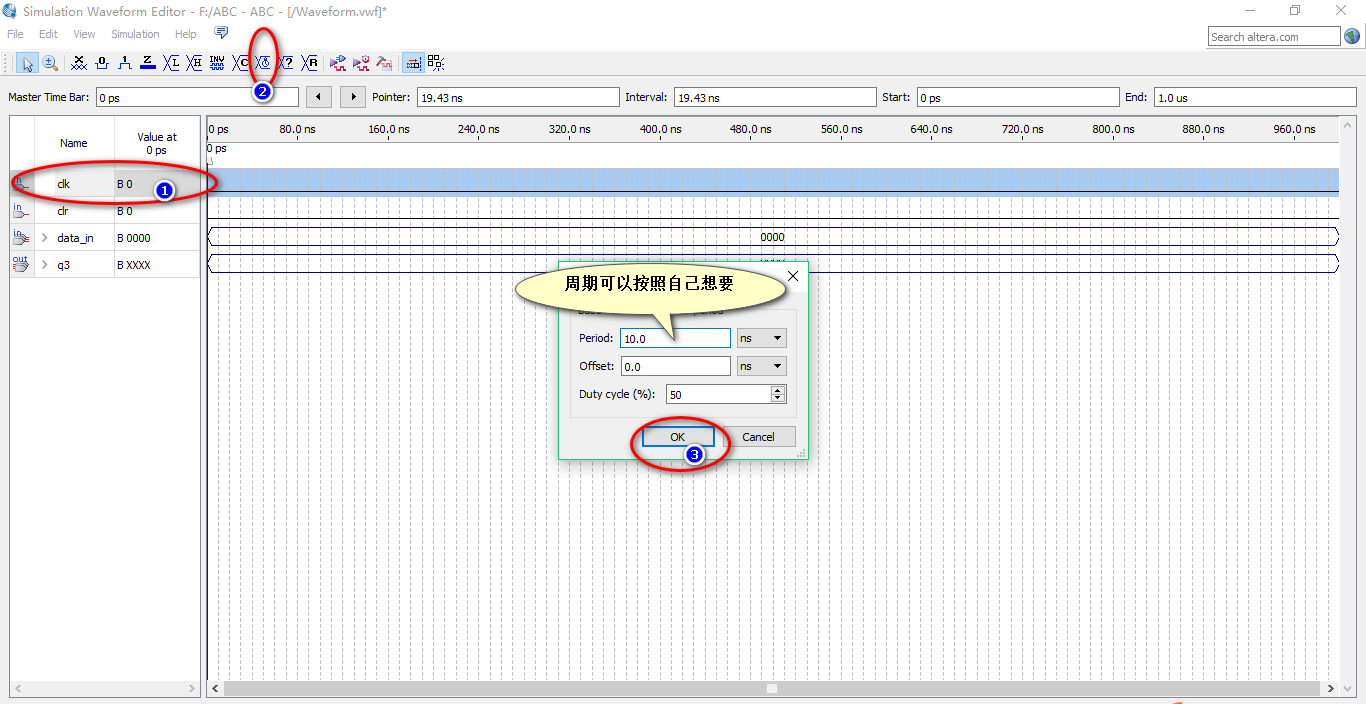

运行成功后,我们开始调波形图,如下图点击file→new根据图示操作

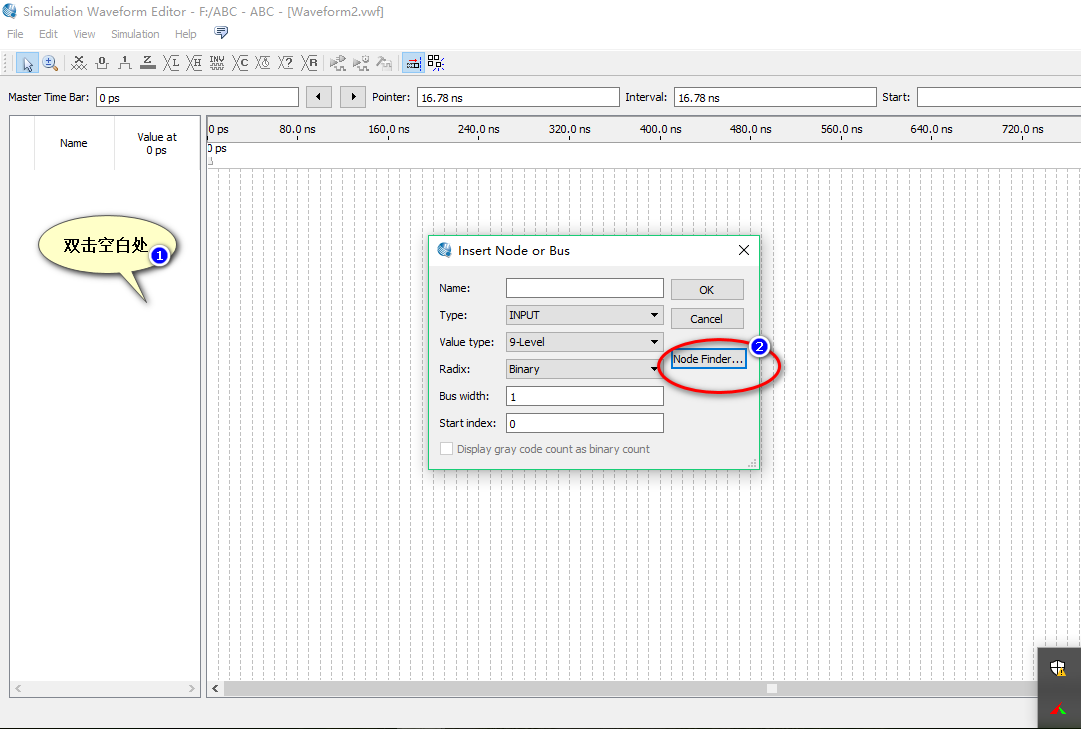

然后再双击图示空白处

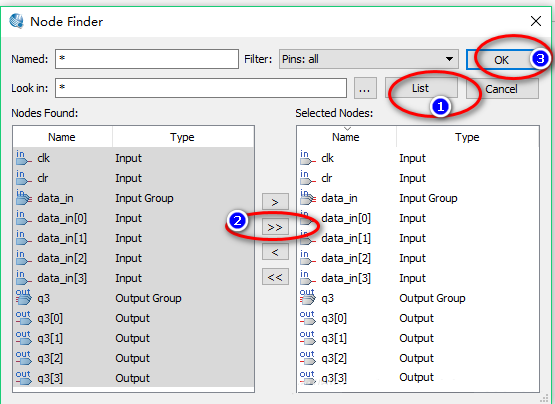

之后点击“ok”

上图①处的下面几个一次按照上面的顺序就可以出图了

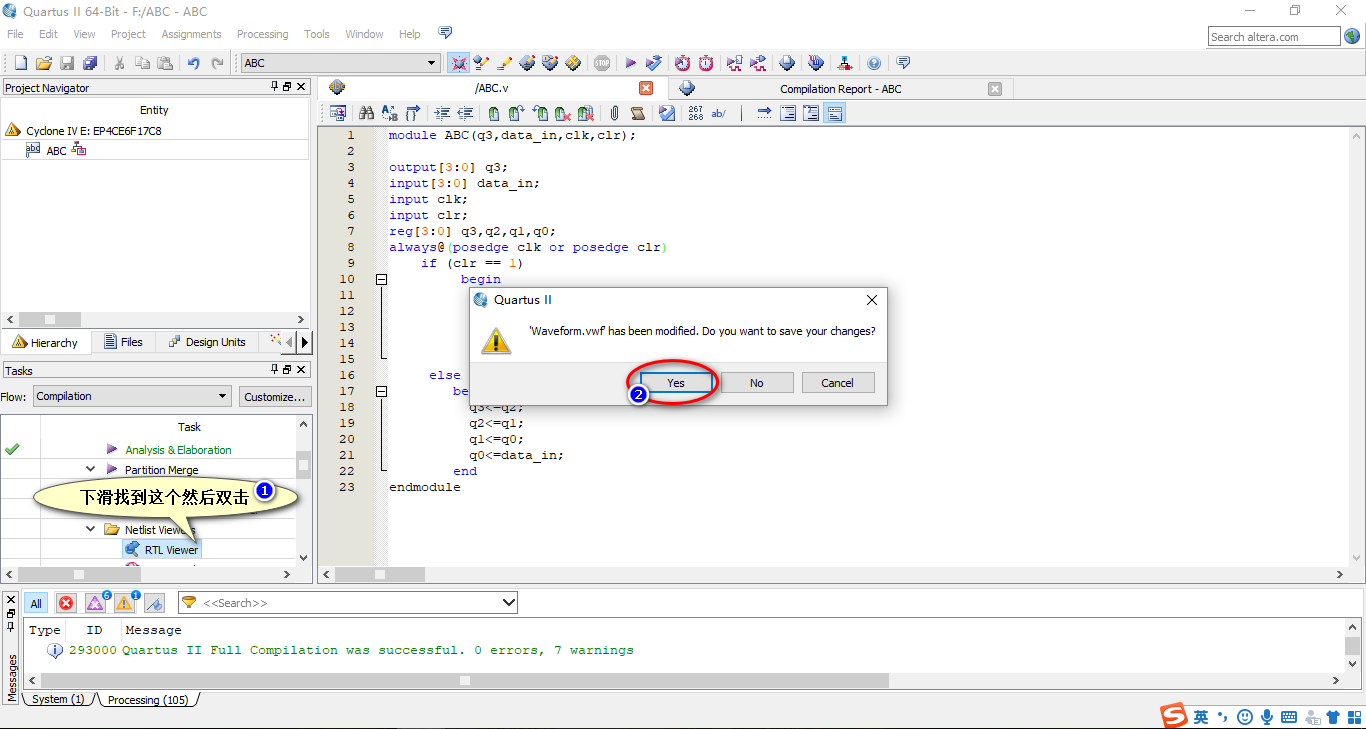

然后在出仿真图,回到最开始的页面

软件会自动弹出保存框,不要改变位置点击“保存”即可

最高点击“OK”就保存成功了